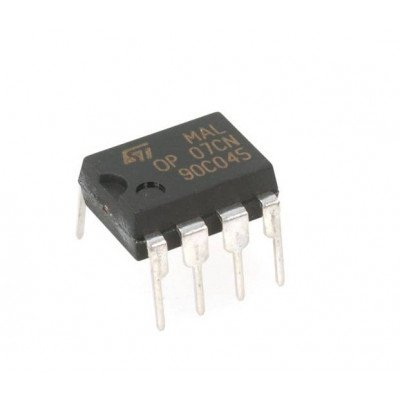

OP07 Ultralow Offset Voltage Op-Amp IC DIP-8 Package

The OP07 has very low input offset voltage (75 ?V maximum for OP07E) that is obtained by trimming at the wafer stage. These low offset voltages generally eliminate any need for external nulling. The OP07 also features low input bias current (?4 nA for the OP07E) and high open-loop gain (200 V/mV for the OP07E). The low offset and high open-loop gain make the OP07 particularly useful for high gain instrumentation applications.

Apple Shopping Event

Hurry and get discounts on all Apple devices up to 20%

Sale_coupon_15

₹23.60

Inclusive of GST

- Pick up from the Robotwala Store

To pick up today

Free

- Shiprocket from Air

Our courier will deliver to the specified address

3-4 Days

139

- Shiprocket from Surface

courier will deliver to the specified address

5-7 Days

90

- Warranty 1 year

- Free 30-Day returns

Payment Methods:

Description

The OP07 has very low input offset voltage (75 ?V maximum for OP07E) that is obtained by trimming at the wafer stage. These low offset voltages generally eliminate any need for external nulling. The OP07 also features low input bias current (?4 nA for the OP07E) and high open-loop gain (200 V/mV for the OP07E). The low offset and high open-loop gain make the OP07 particularly useful for high gain instrumentation applications.

The wide input voltage range of ?13 V minimum combined with a high CMRR of 106 dB (OP07E) and high input impedance provide high accuracy in the non inverting circuit configuration. Excellent linearity and gain accuracy can be maintained even at high closed-loop gains. Stability of offsets and gain with time or variations in temperature is excellent. The accuracy and stability of the OP07, even at high gain, combined with the freedom from external nulling have made the OP07 an industry standard for instrumentation applications. The OP07 is available in two standard performance grades. The OP07E is specified for operation over the 0?C to 70?C range, and the OP07C is specified over the ?40?C to +85?C temperature range. The OP07 is available in epoxy 8-lead PDIP and 8-lead narrow SOIC packages. For CERDIP and TO-99 packages and standard microcircuit drawing (SMD) versions, see the OP77.

Features:-

? Low VOS: 75 ?V (max.)

? Low VOS drift: 1.3 ?V/?C (max.)

? Ultrastable vs. time: 1.5 ?V/month (max.)

? Low noise: 0.6 ?V p-p (max.)

? Wide input voltage range: ?14 V

? Wide supply voltage range: ?3 V to ?18 V

? Fits 725, 108A/308A, 741, and AD510 sockets

? 125?C temperature-tested dice

Specification:-

| Parameter | Specification |

| Supply Voltage (VS) | ?22 V |

| Input Voltage | ?22 V |

| Differential Input Voltage | ?30 V |

| Output Short-Circuit Duration | Indefinite |

| Storage Temperature Range | ?65?C to +125?C |

| Operating Temperature Range | 0?C to 70?C |

| Junction Temperature | 150?C |

| Lead Temperature, Soldering (60 sec) | 300?C |

Related Document:-

Additional information

Operating voltage | 2.5 3.0V |

Pixel Resolution | 0.3MP |

Photosensitive array | 640 x 480 |

Optical Size | 1.6 inch |

Angel of view | 67 degrees |

Maximum Frame Rate | 30fps VGA |

Sensitivity | 1.3V/(Lux-sec) |

Dormancy | Less than 20A |

Power consumption | 60mW/15fpsVGA YUV |

Temperature operation Range | -30 C ~ 70 C |

Pixel area | 3.6 x 3.6 m |

Signal to noise ratio (SNR) | 46 dB |

Dynamic range | 52 dB |

Boards & Modules

Boards & Modules ARM Microcontroller

ARM Microcontroller AVR Microcontroller Board

AVR Microcontroller Board Arduino boards

Arduino boards Advance Development Boards

Advance Development Boards 8051 Development Board

8051 Development Board

Audio Amplifier Module

Audio Amplifier Module Current & Volatage Sensor

Current & Volatage Sensor Breakout Board

Breakout Board Flame Sensors

Flame Sensors Force Sensor

Force Sensor Gas Sensors

Gas Sensors Hall Effect Sensor

Hall Effect Sensor Humidity & Temperature Sensor

Humidity & Temperature Sensor LED Module

LED Module PIR Sensor

PIR Sensor Pressure Sensors

Pressure Sensors Proximity Sensor

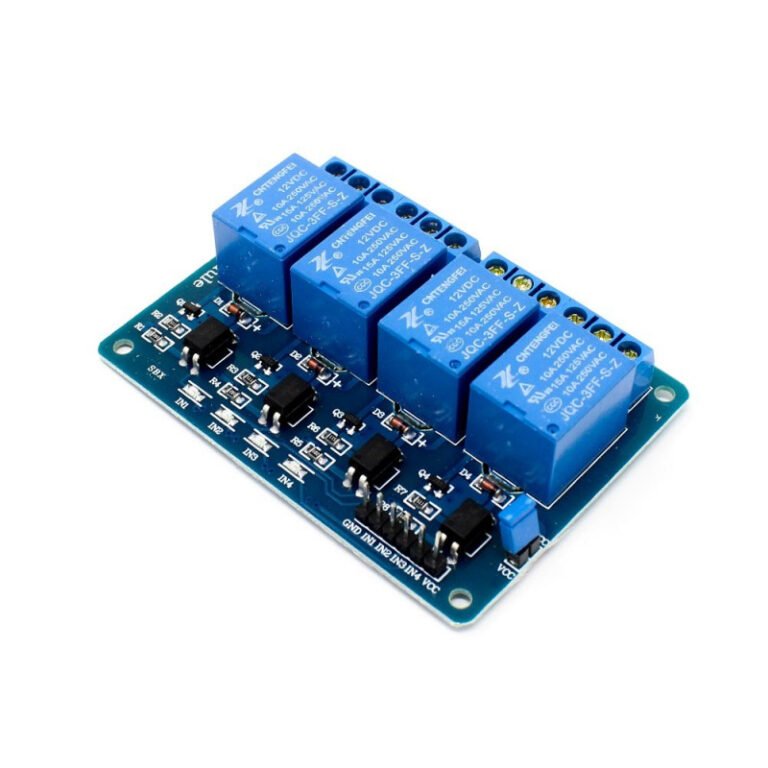

Proximity Sensor Relay Module

Relay Module Real Time Clock (RTC) Module

Real Time Clock (RTC) Module Touch Sensor

Touch Sensor Ultrasonic Sensor

Ultrasonic Sensor Water Level & Water Flow Sensor

Water Level & Water Flow Sensor Weighing Scale Sensor

Weighing Scale Sensor

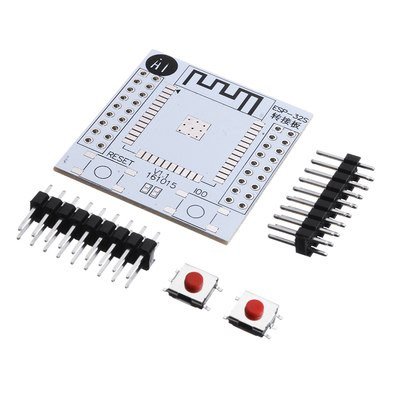

Ai Thinker ESp Wifi Module

Ai Thinker ESp Wifi Module Pic Devlopment Board & programmer

Pic Devlopment Board & programmer Led lights & Strips

Led lights & Strips PCBs & Breadboard

PCBs & Breadboard Potentiometer

Potentiometer Power Transistors

Power Transistors Resistor & Smd & inductor

Resistor & Smd & inductor Switches

Switches Aluminium Heat Sink

Aluminium Heat Sink Buzzer & Speaker

Buzzer & Speaker capacitor

capacitor Crystal Oscillators

Crystal Oscillators Doides

Doides Electric Fuses

Electric Fuses ICs & Dips

ICs & Dips Power supply module

Power supply module Transformer

Transformer Relay Module

Relay Module Kits

Kits Magnet

Magnet RF Connectors

RF Connectors PCT and DC Connectors

PCT and DC Connectors Wires & Heat Shrink

Wires & Heat Shrink FFC, FPC, Berg connectors

FFC, FPC, Berg connectors

Nextion

Nextion Segment

Segment Seedstudio

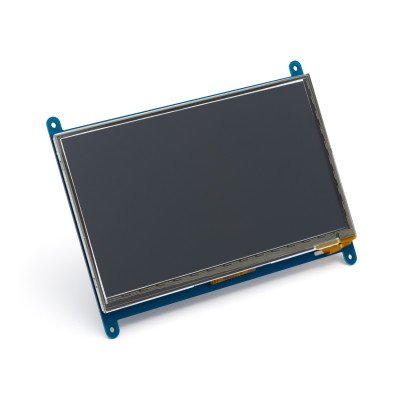

Seedstudio Waveshare

Waveshare E Bike Batteries

E Bike Batteries E bike Battery Case

E bike Battery Case E bike Connectors

E bike Connectors E bike Display

E bike Display E bike Kit

E bike Kit E bike Motors & Controllers

E bike Motors & Controllers Electronics Accessories

Electronics Accessories Mechanical Accessories

Mechanical Accessories

Display

Display Cameras

Cameras

Reviews

There are no reviews yet.