Showing 1213–1224 of 2445 results

Electronic Components

“74HC137 IC – (SMD Package) – 3-to-8 line Decoder/Demultiplexer IC (74138 IC)” has been added to your cart. View cart

74HC109 IC – (SMD Package) – Dual J-K Positive-Edge-Triggered Flip-Flops IC (74109 IC)

₹25.96

The 74HC109 is a dual positive edge triggered JK flip-flop featuring individual nJ and nK inputs. It has clock (nCP) inputs, set (nSD) and reset (nRD) inputs and complementary nQ and nQ outputs. The set and reset are asynchronous active LOW inputs and operate independently of the clock input. The nJ and nK inputs control the state changes of the flip-flops as described in the mode select function table. The nJ and nK inputs must be stable one set-up time prior to the LOW-to-HIGH clock transition for predictable operation. The JK design allows operation as a D-type flip-flop by connecting the nJ and nK inputs together. Inputs include clamp diodes. It enables the use of current limiting resistors to interface inputs to voltages in excess of VCC. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

74HC123 IC – (SMD Package) – Dual Retriggerable Monostable Multivibrator IC (74123)

₹22.42

74HC123 IC – (SMD Package) – Dual Retriggerable Monostable Multivibrator IC (74123)

₹22.42

74HC137 3-to-8 line Decoder/Demultiplexer IC (74138 IC) DIP-16 Package

₹28.32

74HC137 IC – (SMD Package) – 3-to-8 line Decoder/Demultiplexer IC (74138 IC)

₹23.60

74HC137 IC – (SMD Package) – 3-to-8 line Decoder/Demultiplexer IC (74138 IC)

₹23.60

74HC138 3-to-8 line Decoder/Demultiplexer IC (74138 IC) DIP-16 Package

₹17.70

The 74HC138 decoder utilizes advanced silicon-gate CMOS technology and is well suited to memory address decoding or data routing applications. The circuit features high noise immunity and low power consumption usually associated with CMOS circuitry, yet has speeds comparable to low power Schottky TTL logic. The 74HC138 has 3 binary select inputs (A, B, and C). If the device is enabled, these inputs determine which one of the eight normally HIGH outputs will go LOW. Two active LOW and one active HIGH enables (G1, G2A and G2B) are provided to ease the cascading of decoders. The decoder?s outputs can drive 10 low power Schottky TTL equivalent loads, and are functionally and pin equivalent to the 74LS138. All inputs are protected from damage due to static discharge by diodes to VCC and ground.

74HC138 IC – (SMD Package) – 3-to-8 line Decoder/Demultiplexer IC (74138 IC)

₹23.60

The 74HC138 decoder utilizes advanced silicon-gate CMOS technology and is well suited to memory address decoding or data routing applications. The circuit features high noise immunity and low power consumption usually associated with CMOS circuitry, yet has speeds comparable to low power Schottky TTL logic. The 74HC138 has 3 binary select inputs (A, B, and C). If the device is enabled, these inputs determine which one of the eight normally HIGH outputs will go LOW. Two active LOW and one active HIGH enables (G1, G2A and G2B) are provided to ease the cascading of decoders. The decoder?s outputs can drive 10 low power Schottky TTL equivalent loads, and are functionally and pin equivalent to the 74LS138. All inputs are protected from damage due to static discharge by diodes to VCC and ground.

74HC147 IC – (SMD Package) – Decimal to BCD Priority Encoder IC (74147 IC)

₹71.98

The 74HC147 are high speed silicon-gate CMOS devices and are pin-compatible with low power Schottky TTL (LSTTL). The 74HC147 9-input priority encoders accept data from nine active LOW inputs (l1 to l9) and provide binary representation on the four active LOW inputs (Y0 to Y3). A priority is assigned to each input so that when two or more inputs are simultaneously active, the input with the highest priority is represented on the output, with input l9 line having the highest priority. These devices provide the 10-line to 4-line priority encoding function by use of the implied decimal ?zero?. The ?zero? is encoded when all nine data inputs are HIGH, forcing all four outputs HIGH.

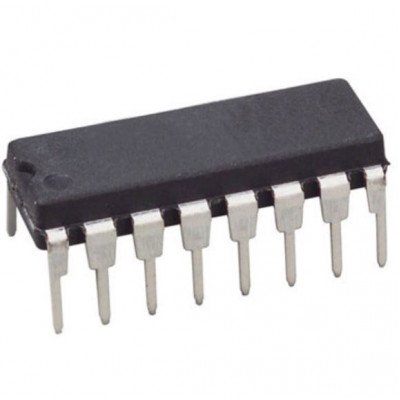

74HC151 8-Input Multiplexer IC (74151 IC) DIP-16 Package

₹24.78

74HC151 is 8 - Input Multiplexer 16 Pin IC. Data Selector/Multiplexer contains full on-chip decoding to select one-of-eight data sources as a result of a unique three binary code at select inputs. Two complementary outputs provide both inverting and non-inverting buffer operation. A Strobe input is provided which, when at high level, disables all data inputs and forces Y output to low state and W output to high state. Select input buffers incorporate internal overlap features to ensure that select input changes do not cause invalid output transients.Used for Boolean Function Generator.

74HC151 IC – (SMD Package) – 8 – Input Multiplexer IC (74151 IC)

₹28.32

The 74HC151 high speed Digital multiplexer utilizes advanced silicon-gate CMOS technology. Along with the high noise immunity and low power dissipation of standard CMOS integrated circuits, it possesses the ability to drive 10 LS-TTL loads. The 74HC151 selects one of the 8 data sources, depending on the address presented on the A, B, and C inputs. It features both true (Y) and complement (W) outputs. The STROBE input must be at a low logic level to enable this multiplexer. A high logic level at the STROBE forces the W output HIGH and the Y output LOW. The 74HC logic family is functionally as well as pin-out compatible with the standard 74LS logic family. All inputs are protected from damage due to static discharge by internal diode clamps to VCC and ground.

Boards & Modules

Boards & Modules ARM Microcontroller

ARM Microcontroller AVR Microcontroller Board

AVR Microcontroller Board Arduino boards

Arduino boards Advance Development Boards

Advance Development Boards 8051 Development Board

8051 Development Board

Audio Amplifier Module

Audio Amplifier Module Current & Volatage Sensor

Current & Volatage Sensor Breakout Board

Breakout Board Flame Sensors

Flame Sensors Force Sensor

Force Sensor Gas Sensors

Gas Sensors Hall Effect Sensor

Hall Effect Sensor Humidity & Temperature Sensor

Humidity & Temperature Sensor LED Module

LED Module PIR Sensor

PIR Sensor Pressure Sensors

Pressure Sensors Proximity Sensor

Proximity Sensor Relay Module

Relay Module Real Time Clock (RTC) Module

Real Time Clock (RTC) Module Touch Sensor

Touch Sensor Ultrasonic Sensor

Ultrasonic Sensor Water Level & Water Flow Sensor

Water Level & Water Flow Sensor Weighing Scale Sensor

Weighing Scale Sensor

Ai Thinker ESp Wifi Module

Ai Thinker ESp Wifi Module Pic Devlopment Board & programmer

Pic Devlopment Board & programmer Led lights & Strips

Led lights & Strips PCBs & Breadboard

PCBs & Breadboard Potentiometer

Potentiometer Power Transistors

Power Transistors Resistor & Smd & inductor

Resistor & Smd & inductor Switches

Switches Aluminium Heat Sink

Aluminium Heat Sink Buzzer & Speaker

Buzzer & Speaker capacitor

capacitor Crystal Oscillators

Crystal Oscillators Doides

Doides Electric Fuses

Electric Fuses ICs & Dips

ICs & Dips Power supply module

Power supply module Transformer

Transformer Relay Module

Relay Module Kits

Kits Magnet

Magnet RF Connectors

RF Connectors PCT and DC Connectors

PCT and DC Connectors Wires & Heat Shrink

Wires & Heat Shrink FFC, FPC, Berg connectors

FFC, FPC, Berg connectors

Nextion

Nextion Segment

Segment Seedstudio

Seedstudio Waveshare

Waveshare E Bike Batteries

E Bike Batteries E bike Battery Case

E bike Battery Case E bike Connectors

E bike Connectors E bike Display

E bike Display E bike Kit

E bike Kit E bike Motors & Controllers

E bike Motors & Controllers Electronics Accessories

Electronics Accessories Mechanical Accessories

Mechanical Accessories

Display

Display Cameras

Cameras