Showing 1381–1392 of 2445 results

Electronic Components

“74LS14 IC – (SMD Package) Hex Schmitt Trigger Inverter IC (7414 IC)” has been added to your cart. View cart

74LS125 Quad Tri-state Buffer IC (74125 IC) DIP-14 Package

₹21.24

This device contains four independent gates each of which performs a non-inverting buffer function. The outputs have the 3-STATE feature. When enabled, the outputs exhibit the low impedance characteristics of a standard LS output with additional drive capability to permit the driving of bus lines without external resistors. When disabled, both the output transistors are turned off presenting a high-impedance state to the bus line. Thus the output will act neither as a significant load nor as a driver. To minimize the possibility that two outputs will attempt to take a common bus to opposite logic levels, the disable time is shorter than the enable time of the outputs.

74LS126 Quad 3-State Buffer IC (74126 IC) DIP-14 Package

₹20.06

74LS13 Schmitt Trigger IC (7413 IC) DIP-14 Package

₹41.30

The 74LS13 contain logic gates/inverters which accept standard TTL input signals and provide standard TTL output levels. They are capable of transforming slowly changing input signals into sharply defined, jitter-free output signals. Additionally, they have greater noise margin than conventional inverters. Each circuit contains a Schmitt trigger followed by a Darlington level shifter and a phase splitter driving a TTL totem pole output. The Schmitt trigger uses positive feedback to effectively speed-up slow input transitions, and provide different input threshold voltages for positive and negative-going transitions. This hysteresis between the positive-going and negative-going input thresholds (typically 800 mV) is determined internally by resistor ratios and is essentially insensitive to temperature and supply voltage variations.

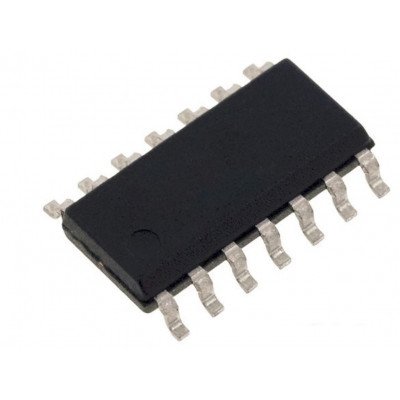

74LS132 IC – (SMD Package) Quad 2-Input Schmitt Trigger IC (74132 IC)

₹28.32

74LS132 Quad 2-Input Schmitt Trigger IC (74132 IC) DIP-14 Package

₹38.94

74LS138 1-of-8 Decoder/Demultiplexer IC (74138) DIP-16 Package

₹53.10

These Schottky-clamped circuits are designed to be used in high-performance memory-decoding or data-routing applications, requiring very short propagation delay times. In high-performance memory systems these decoders can be used to minimize the effects of system decoding. When used with high-speed memories, the delay times of these

74LS138 IC – (SMD Package) 1-to-8 Decoder/Demultiplexer IC (74138 IC)

₹46.02

These Schottky-clamped circuits are designed to be used in high-performance memory-decoding or data-routing applications, requiring very short propagation delay times. In high-performance memory systems these decoders can be used to minimize the effects of system decoding. When used with high-speed memories, the delay times of these decoders are usually less than the typical access time of the memory. This means that the effective system delay introduced by the decoder is negligible. The 74LS138 decodes one-of-eight lines, based upon the conditions at the three binary select inputs and the three enable inputs. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented with no external inverters, and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.

74LS139 Dual 2-to-4 line Decoder/Demultiplexer IC (74139 IC) DIP-16 Package

₹29.50

The 74LS139 comprises two separate two-line-to-four line decoders in a single package. The active-low enable input can be used as a data line in demultiplexing applications. All of these decoders/demultiplexers feature fully buffered inputs, presenting only one normalized load to its driving circuit. All inputs are clamped with high-performance Schottky diodes to suppress line-ringing and simplify system design.

74LS139 IC – (SMD Package) – High Speed Dual 1-of-4 Decoder/De-multiplexer IC (74139 IC)

₹34.22

The 74LS139 is a clamped circuits are designed to be used in high-performance memory-decoding or data-routing applications, requiring very short propagation delay times. In high-performance memory systems these decoders can be used to minimize the effects of system decoding. When used with high-speed memories, the delay times of these decoders are usually less than the typical access time of the memory. This means that the effective system delay introduced by the decoder is negligible. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented with no external inverters, and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications. The 74LS139 comprises two separate two-line-to-fourline decoders in a single package. The active-low enable input can be used as a data line in demultiplexing applications. All of these decoders/demultiplexers feature fully buffered inputs, presenting only one normalized load to its driving circuit. All inputs are clamped with high-performance Schottky diodes to suppress line-ringing and simplify system design.

74LS14 Hex Schmitt Trigger Inverter IC (7414 IC) DIP-14 Package

₹17.70

74LS14 IC – (SMD Package) Hex Schmitt Trigger Inverter IC (7414 IC)

₹29.50

74LS147 Decimal to BCD Priority Encoder IC (74147 IC) DIP-16 Package

₹62.54

The 74LS147 TTL encoders feature priority decoding of the inputs to ensure that only the highest-order data line is encoded. The ?147 and ?LS147 devices encode nine data lines to four-line (8-4-2-1) BCD. The implied decimal zero condition requires no input condition, as zero is encoded when all nine data lines are at a high logic level. Cascading circuitry (enable input EI and enable output EO) has been provided to allow octal expansion without the need for external circuitry. For all types, data inputs and outputs are active at the low logic level.

Boards & Modules

Boards & Modules ARM Microcontroller

ARM Microcontroller AVR Microcontroller Board

AVR Microcontroller Board Arduino boards

Arduino boards Advance Development Boards

Advance Development Boards 8051 Development Board

8051 Development Board

Audio Amplifier Module

Audio Amplifier Module Current & Volatage Sensor

Current & Volatage Sensor Breakout Board

Breakout Board Flame Sensors

Flame Sensors Force Sensor

Force Sensor Gas Sensors

Gas Sensors Hall Effect Sensor

Hall Effect Sensor Humidity & Temperature Sensor

Humidity & Temperature Sensor LED Module

LED Module PIR Sensor

PIR Sensor Pressure Sensors

Pressure Sensors Proximity Sensor

Proximity Sensor Relay Module

Relay Module Real Time Clock (RTC) Module

Real Time Clock (RTC) Module Touch Sensor

Touch Sensor Ultrasonic Sensor

Ultrasonic Sensor Water Level & Water Flow Sensor

Water Level & Water Flow Sensor Weighing Scale Sensor

Weighing Scale Sensor

Ai Thinker ESp Wifi Module

Ai Thinker ESp Wifi Module Pic Devlopment Board & programmer

Pic Devlopment Board & programmer Led lights & Strips

Led lights & Strips PCBs & Breadboard

PCBs & Breadboard Potentiometer

Potentiometer Power Transistors

Power Transistors Resistor & Smd & inductor

Resistor & Smd & inductor Switches

Switches Aluminium Heat Sink

Aluminium Heat Sink Buzzer & Speaker

Buzzer & Speaker capacitor

capacitor Crystal Oscillators

Crystal Oscillators Doides

Doides Electric Fuses

Electric Fuses ICs & Dips

ICs & Dips Power supply module

Power supply module Transformer

Transformer Relay Module

Relay Module Kits

Kits Magnet

Magnet RF Connectors

RF Connectors PCT and DC Connectors

PCT and DC Connectors Wires & Heat Shrink

Wires & Heat Shrink FFC, FPC, Berg connectors

FFC, FPC, Berg connectors

Nextion

Nextion Segment

Segment Seedstudio

Seedstudio Waveshare

Waveshare E Bike Batteries

E Bike Batteries E bike Battery Case

E bike Battery Case E bike Connectors

E bike Connectors E bike Display

E bike Display E bike Kit

E bike Kit E bike Motors & Controllers

E bike Motors & Controllers Electronics Accessories

Electronics Accessories Mechanical Accessories

Mechanical Accessories

Display

Display Cameras

Cameras